## L6254

## **SPINDLE**

**PRODUCT PREVIEW**

## **FEATURES:**

## **Spindle Motor Driver**

- Internal 4A peak current power drivers.

- Low Rds(on) 0.28 ohms maximum at 25°C.

- External current sense resistor.

- Slew rate control of both upper and lower drivers.

- Programmable linear or switch mode current driver.

- Constant off-time switch mode spindle power driver.

- Upper and lower drivers soft switching value externally set.

- Provide spindle active dynamic braking mode.

- Programmable spindle braking during power down condition.

- 15 KHz minimum spindle current control loop bandwidth.

## **Voice Coil Motor Driver and Retract Circuit**

- Internal 2.5A peak current VCM power drivers.

- Low Rds(on) 0.4 ohms maximum at 25°C.

- External current sense resistor.

- External current control loop compensation.

- Zero dead-band and minimum cross over distortion.

- 20KHz minimum VCM current control loob bandwidth.

- Multi quadrant programmable retract down to 5 volts of BEMF.

- Constant hold voltage across the VCM down to 2 volts of BEMF.

## **Power Monitor and Negative Voltage Regulator**

- +5 volts and +12 volts power monitor threshold accuracy +/-2%.

- Hysteresis on both power monitor comparator.

- Precision internal voltage generator +/-2%.

- Buffered reference voltage output pin.

- Thermal sense circuit and an over temperature shut down.

- Internal booster voltage generator.

- Internal constant frequency switch mode voltage regulator for a negative power supply.

## **GENERAL DESCRIPTION**

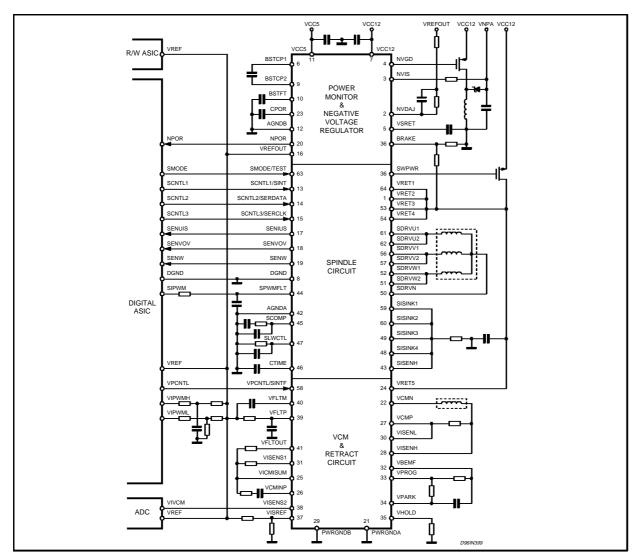

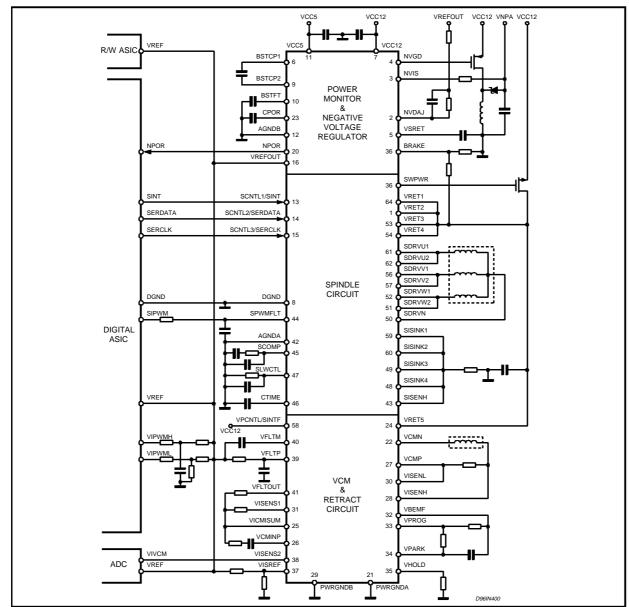

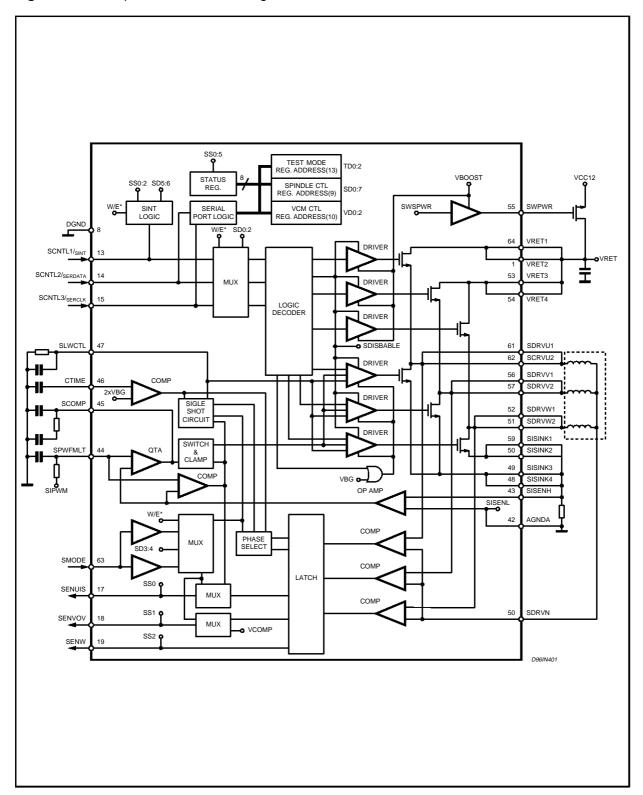

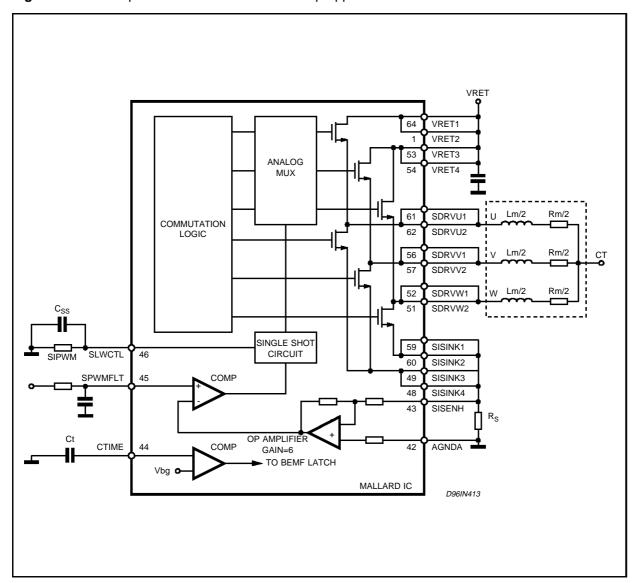

L6254 is a mixed signal ASIC that includes spindle motor driver, voice coil motor driver, retract circuit, brake circuit, power monitor and a negative voltage power supply voltage regulator.

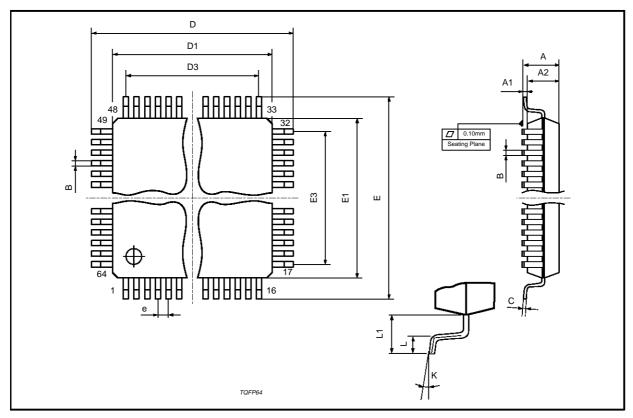

The L6254 IC (Figure 1) is packaged in a 64 pin TQFP with Metal Slug for improved dissipation.

June 1996 1/30

## **PIN DESCRIPTION**

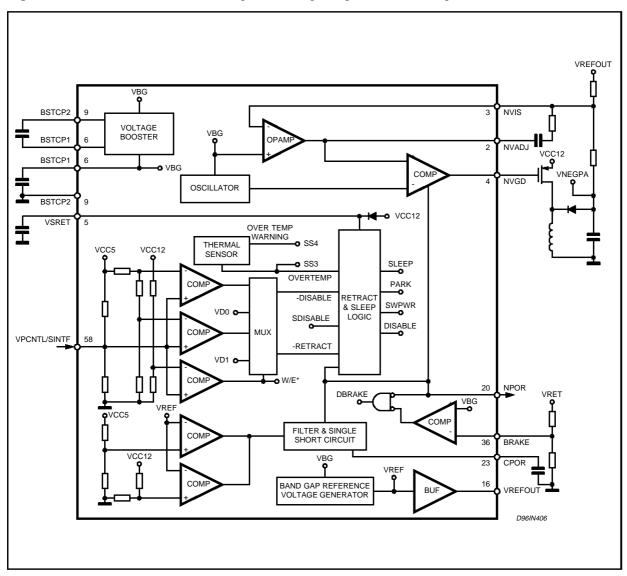

## Power Monitor and Negative Voltage Regulator Circuit.

| Number | Signal Name | Туре | Functional Description                                                                                                                                                                                                                                      |

|--------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11     | VCC5        | IP   | +5V power supply.                                                                                                                                                                                                                                           |

| 07     | VCC12       | IP   | +12V power supply.                                                                                                                                                                                                                                          |

| 12     | AGNDB       | IP   | Analog ground.                                                                                                                                                                                                                                              |

| 06     | BSTCP1      | OA   | Booster input capacitor terminal 1.                                                                                                                                                                                                                         |

| 09     | BSTCP2      | IA   | Booster input capacitor terminal 2.                                                                                                                                                                                                                         |

| 10     | BSTFLT      | OA   | Charge pump booster output capacitor.                                                                                                                                                                                                                       |

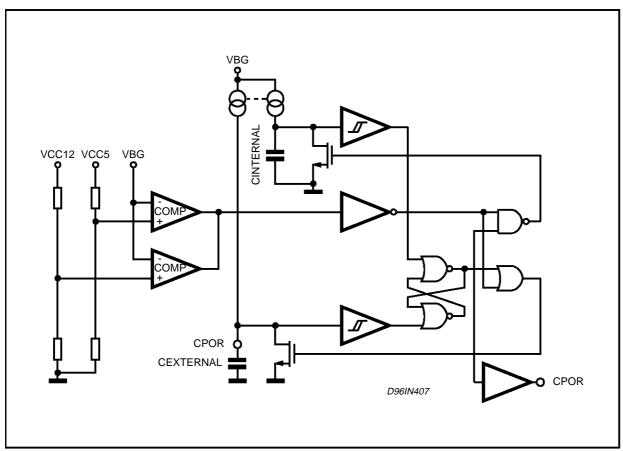

| 23     | CPOR        | IA   | A capacitor is placed on this pin to program the power on reset delay.                                                                                                                                                                                      |

| 20     | NPOR        | OD   | Power on reset active low logic signal.                                                                                                                                                                                                                     |

| 58     | VPCNTRL     | IZ   | VCM driver enable mode of operation control. With the aid of an internal resistor divider VPCNTRL delivers three logic states.  L = retract, H = enable, Z = disable. When V <sub>CC12</sub> is connected to this pin the serial interface mode is enabled. |

| 05     | VSRET       | IA   | Reservoir capacitor is placed here to provide retract control voltage during BRAKE.                                                                                                                                                                         |

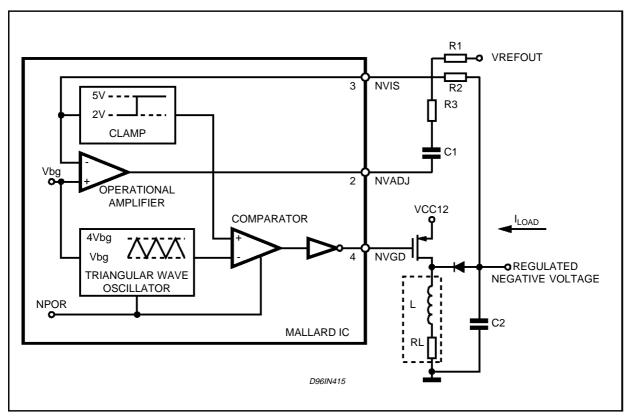

| 04     | NVGD        | IA   | Negative voltage regulator external PFET gate control voltage.                                                                                                                                                                                              |

| 02     | VNVADJ      | OA   | Negative voltage regulator error amplifier output.                                                                                                                                                                                                          |

| 03     | NVIS        | IA   | Negative voltage regulator error amplifier summing junction.                                                                                                                                                                                                |

| 36     | BRAKE       | IA   | Spindle brake activation threshold during power loss.                                                                                                                                                                                                       |

| 16     | VREFOUT     | OA   | An internal 4V voltage reference buffered output.                                                                                                                                                                                                           |

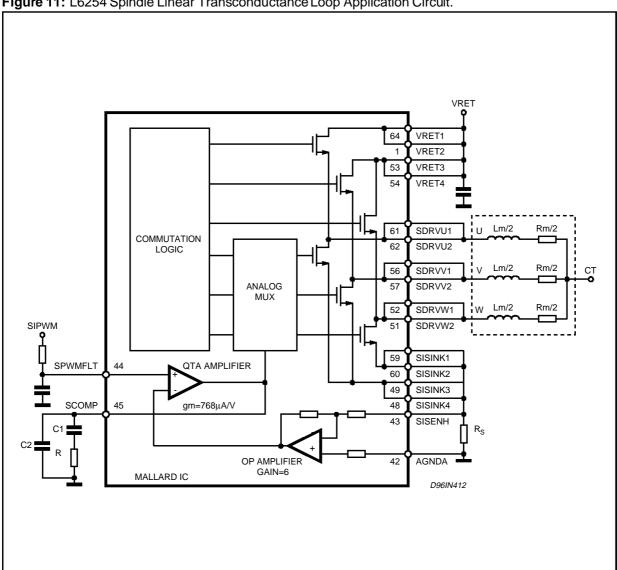

## Spindle Circuit.

| Number | Signal Name | Туре | Functional Description                                                                                                                 |

|--------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 61     | SDRVU1      | OA   | Spindle motor coil terminal phase U.                                                                                                   |

| 62     | SDRVU2      | OA   | Spindle motor coil terminal phase U.                                                                                                   |

| 56     | SDRVV1      | OA   | Spindle motor coil terminal phase V.                                                                                                   |

| 57     | SDRVV2      | OA   | Spindle motor coil terminal phase V.                                                                                                   |

| 52     | SDRVW1      | OA   | Spindle motor coil terminal phase W.                                                                                                   |

| 51     | SDRVW2      | OA   | Spindle motor coil terminal phase W.                                                                                                   |

| 64     | VRET1       | IA   | 3 phase power driver bridge input power. During power failure condition this pin provide the full wave rectified spindle BEMF voltage. |

| 01     | VRET2       | IA   | 3 phase power driver bridge input power. During power failure condition this pin provide the full wave rectified spindle BEMF voltage. |

| 53     | VRET3       | IA   | 3 phase power driver bridge input power. During power failure condition this pin provide the full wave rectified spindle BEMF voltage. |

| 54     | VRET4       | IA   | 3 phase power driver bridge input power. During power failure condition this pin provide the full wave rectified spindle BEMF voltage. |

| 59     | SISINK1     | OA   | 3 phase power driver bridge sink output.                                                                                               |

| 60     | SISINK2     | OA   | 3 phase power driver bridge sink output.                                                                                               |

| 49     | SISINK3     | OA   | 3 phase power driver bridge sink output.                                                                                               |

| 48     | SISINK4     | OA   | 3 phase power driver bridge sink output.                                                                                               |

| 43     | SISENH      | IA   | External current sense resistor terminal. The other terminal of the current sense resistor must be connected to AGNDA.                 |

| 42     | AGNDA       | IP   | Analog ground.                                                                                                                         |

| 55     | SWPWR       | OA   | High voltage external power isolation NFET transistor gate control.                                                                    |

## PIN DESCRIPTION (continued)

## Spindle Circuit (continued)

| Number | Signal Name        | Туре  | Functional Description                                                                                                                                                                                         |

|--------|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50     | SDRVN              | IA    | Spindle motor center tap.                                                                                                                                                                                      |

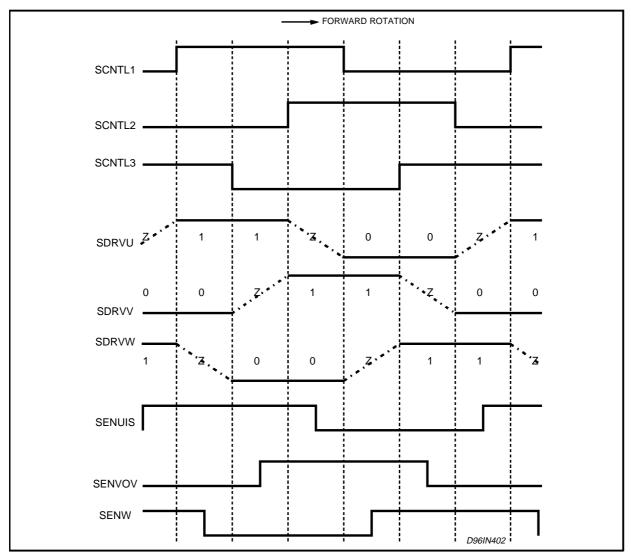

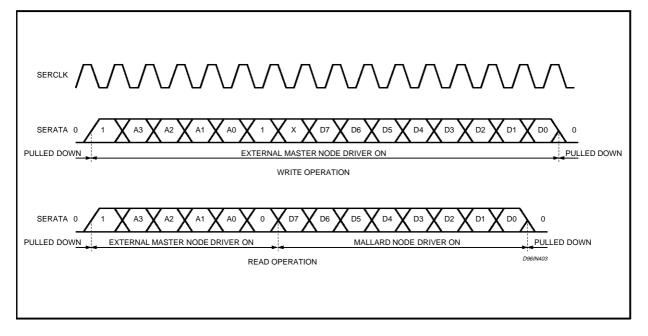

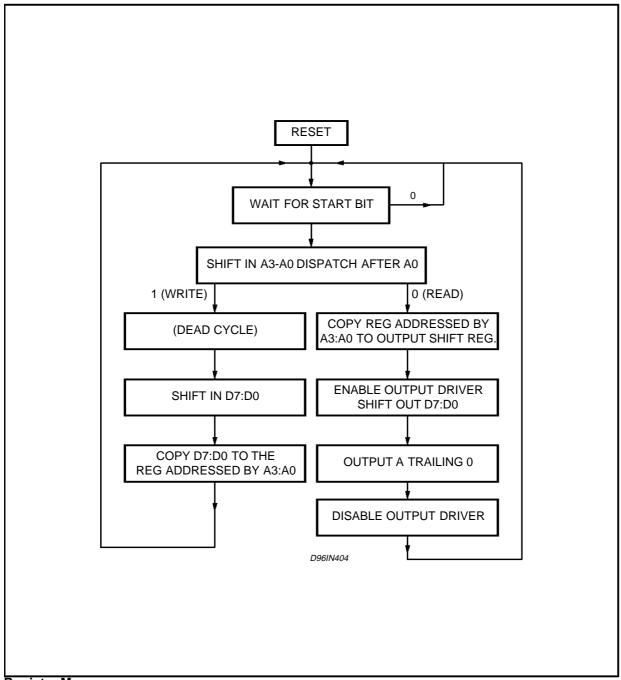

| 13     | SCNTL1/SINT        | I/OD  | Spindle state control bit 0 in the parallel interface mode and muxed BEMF comparator output in the serial interface mode.                                                                                      |

| 14     | SCNTL2/<br>SERDATA | I/O D | Spindle state control bit 1 in the parallel interface mode and serial data input/output in the serial interface mode.                                                                                          |

| 15     | SCNTL3/<br>SERCLK  | ID    | Spindle state control bit 2 in the parallel interface mode and the serial interface clock input in the serial interface mode.                                                                                  |

| 8      | DGND               | IA    | Digital ground.                                                                                                                                                                                                |

| 17     | SENUIS             | OD    | Spindle motor phase U BEMF comparator output or current comparator output controlled by the SMODE pin.                                                                                                         |

| 18     | SENVOV             | OD    | Spindle motor phase V comparator output or VCM offset voltage comparator controlled by the SMODE pin.                                                                                                          |

| 19     | SENW               | OD    | Spindle motor phase W BEMF comparator output.                                                                                                                                                                  |

| 63     | SMODE/TEST         | ΙZ    | Spindle driver mode control.  H == BEMF sense & Linear control.  Z == Inductance sense & Linear control.  L == BEMF sense & PWM control  When V <sub>CC12</sub> is connected to this pin test mode is enabled. |

| 44     | SPWMFLT            | IA    | Spindle motor current command analog input.                                                                                                                                                                    |

| 46     | CTIME              | IA    | A capacitor is placed here to limit the on time during switch mode operation.                                                                                                                                  |

| 45     | SCOMP              | OA    | Spindle current control loop compensation.                                                                                                                                                                     |

| 47     | SLWCTL/<br>SSTOFF  | OA    | Slew rate programming for the H bridge upper and lower drivers.                                                                                                                                                |

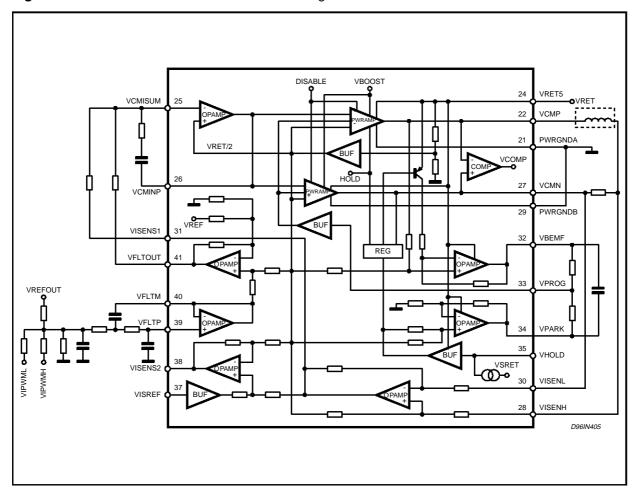

## **Voice Coil Motor Driver and Retract Circuit.**

| Number | Signal Name | Туре | Functional Description                                                                 |

|--------|-------------|------|----------------------------------------------------------------------------------------|

| 39     | VFLTP       | IA   | VCM current command active filter OP AMP plus terminal.                                |

| 40     | VFLTM       | OA   | VCM current command active filter OP AMP minus terminal.                               |

| 41     | VFLTOUT     | OA   | VCM current command filtered output.                                                   |

| 25     | VCMISUM     | IA   | The current control loop error operational amplifier summing junction.                 |

| 26     | VCMINP      | OA   | The current control loop error operational amplifier output.                           |

| 28     | VISENH      | IA   | VCM current sense amplifier input voltage non-inverting side.                          |

| 30     | VISENL      | IA   | VCM current sense amplifier input voltage inverting side.                              |

| 31     | VISENS1     | OA   | VCM current sense amplifier output 1. [Output is around VREFOUT level].                |

| 38     | VISENS2     | OA   | VCM current sense amplifier output 2. [Output around VRET/2].                          |

| 37     | VISREF      | IA   | Reference voltage to set the zero current level of the second current sense amplifier. |

| 27     | VCMP        | OA   | VCM H bridge power driver output non-inverting coil terminal.                          |

| 22     | VCMN        | OA   | VCM H bridge power driver output inverting coil terminal.                              |

| 24     | VRET5       | OA   | VCM power driver H bridge input power.                                                 |

| 21     | PWRGNDA     | OA   | VCM power driver ground return.                                                        |

| 29     | PWRGNDB     | OA   | VCM power driver ground return.                                                        |

| 35     | VHOLD       | IA   | Hold mode programming current.                                                         |

| 34     | VPARK       | IA   | Park circuit programming voltage during four quadrant retract.                         |

| 33     | VPROG       | IA   | VCM control voltage during four quadrant retract.                                      |

| 32     | VBEMF       | OA   | VCM back EMF voltage sense during retract. [Output is around VRET/2]                   |

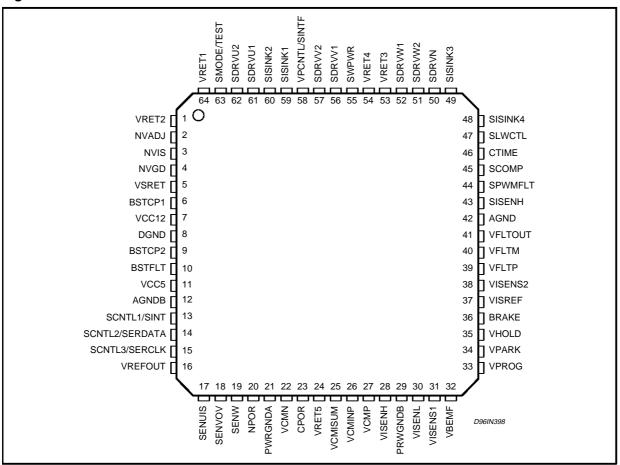

Figure 1: Pin connection.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                       | Value                         | Unit |

|------------------|-------------------------------------------------|-------------------------------|------|

| T <sub>i</sub>   | Junction Temperature                            | +150                          | °C   |

|                  | Power Supply Voltage Vcc12                      | -0.3 to 15                    | V    |

|                  | Power Supply Voltage Vcc5                       | -0.3 to 7                     | V    |

| T <sub>stg</sub> | Storage temperature                             | -55 to +150                   | °C   |

|                  | Digital input voltage pins                      | -0.3V to Vcc5 +0.5            |      |

|                  | Analog input voltage pins                       | -0.3V to Vcc12 +0.5           |      |

|                  | BSTFLT pin                                      | -0.3 to 24                    | V    |

|                  | DC output current SDRVU-W                       | 4                             | Α    |

|                  | DC output current VCMN-P                        | 2.5                           | Α    |

|                  | ESD rating (all pins)                           | 2000                          | V    |

|                  | Latch up rating (all pins)                      | 200 or Absolute Max.<br>Volt. | mA   |

|                  | Total power dissipation T <sub>amb</sub> = 70°C | TBD                           |      |

<u>CAUTION: Devices can suffer permanent damage and or reliability degradation if operated beyond the following maximum rating.</u>

**ELECTRICAL CHARACTERISTICS** (The following specifications apply over the recommended operating ambient temperature range  $T_{amb}=0$  to  $70^{\circ}C$  and the recommended power supplies operating voltage range of  $V_{CC5}=5~V-5\%+10\%~\&~V_{CC12}=12~V+/-10\%$  unless otherwise specified) **Power Monitor and Negative Voltage Regulator**

| Symbol               | Parameter                          | Test Condition                          | Min.   | Тур.  | Max.     | Unit              |

|----------------------|------------------------------------|-----------------------------------------|--------|-------|----------|-------------------|

| POWER SU             | JPPLY CURRENT (Vcc5 & Vcc12)       | )                                       | •      |       |          |                   |

| lcc5                 | +5V Supply current                 | Normal mode                             |        | 7     |          | mA                |

|                      |                                    | Sleep mode                              |        | 7     |          | mA                |

| lcc12                | +12V Supply current.               | Normal mode                             |        | 21    |          | mA                |

| VOLTAGE              | DEFENDENCE (VIDEEOUT)              | Sleep mode                              |        | 11    | <u> </u> | mA                |

|                      | REFERENCE (VREFOUT)                | Dlood : 4000                            | 1 2.02 | 1 4   | 1 4 00   | Ιv                |

| Vref                 | Voltage at VREFOUT                 | Rload > 400Ω<br>Cload < 0.1μF           | 3.92   | 4     | 4.08     | V                 |

| Irefouh              | Source current                     |                                         | 10     |       |          | mA                |

| Irefoul              | Sink current                       |                                         | 1      |       |          | mA                |

| PSRR                 | Power supply rejection ratio       | f < 10kHz, ripple < 0.3V                | 50     |       | ļ        | dB                |

| $L_{REG}$            | Load Regulation                    | $V_{REFOUT} = 4V$ $I_{OUT} = 0$ to 10mA |        |       | 0.5%     | %V <sub>OUT</sub> |

| VOLTAGE              | <b>BOOSTER (BSTCP1 BSTCP2 BS</b>   | TFLT)                                   |        |       |          |                   |

| Vcp                  | Change pump voltage                | Vcc12 = 10.8:13.2V                      | 18     |       | 24       | V                 |

| lint                 | Internal load current              |                                         |        |       | 950      | μА                |

| lload                | Max. external load.                | Vcp = Vcp initial - 0.2V                |        |       | 1        | mA                |

|                      | Short circuit output current       | pin BSTFL                               |        |       | 300      | mA                |

| AUXILIARY            | RETRACT POWER SUPPLY (VS           | SRET)                                   |        |       |          |                   |

| I <sub>leakage</sub> | Leakage current at VSRET           |                                         |        |       | 100      | nA                |

|                      | ONITOR COMPARATORS                 | •                                       |        |       |          |                   |

| Vt5                  | +5V Threshold voltage              |                                         | TBD    | 4.625 | TBD      | V                 |

| Hv5                  | Hysteresis on Vcc5 comp.           |                                         | 50     | 75    | 100      | mV                |

| Vt12                 | +12V Threshold voltage.            |                                         | 9.7    | 10.10 | 10.50    | V                 |

| Hv12                 | Hystetesis on Vcc12 comp.          |                                         | 100    | 140   | 180      | mV                |

| POWER OF             | N RESET GENERATOR (CPOR A          | ND NPOR)                                | •      |       |          |                   |

| Icpor                | CPOR charge current                | T                                       | 2      |       | 4        | μА                |

| Vtpor                | Trigger voltage                    | Vcc5 = +5V                              | 2.2    | 2.5   | 2.8      | V                 |

| Tpfmin               | Power fault time that trigger POR. |                                         | 8      |       | 20       | μS                |

| Vlow                 | NPOR low level voltage             | Isink = 2mA                             |        |       | 0.4      | V                 |

| Vhigh                | NPOR high level voltage            |                                         | 3.5    |       |          | V                 |

| ttr                  | NPOR transition time               | cload = 50pF                            |        |       | 30       | ns                |

| OVER TEM             | PERATURE PROTECTION                |                                         | •      | •     | •        | •                 |

| Twam                 | Thermal warming temperature        | guaranteed by design                    | 130    | 140   | 150      | °C                |

| Tsoft                | Switch off temperature             | 1                                       | 150    | 160   | 170      | °C                |

| Thyst                | Thermal Hysteresis                 | 1                                       | 20     |       | 30       | °C                |

| NEGATIVE             | VOLTAGE REGULATOR OPAME            | (NVIS, NVADJ)                           |        | -     | -        | -                 |

|                      | Gain                               | 1                                       |        | 60    |          | dB                |

|                      | Bandwidth                          |                                         |        | 1     |          | MHz               |

|                      | Input offset                       |                                         |        | 3     |          | mV                |

|                      | Input bias                         |                                         |        | 1     | 2        | μΑ                |

| NEGATIVE             | VOLTAGE REGULATOR COMPA            | ARATOR (NVGD)                           |        | •     | •        |                   |

|                      | Hysteresis                         | T , ,                                   |        | 60    |          | mV                |

|                      | Output swing                       |                                         | 0      |       | 12       | V                 |

|                      | Output transition                  | C <sub>L</sub> = 600pF                  |        | 150   |          | ns                |

| Voff                 | Output voltage during NPOR         | 1 ~ '                                   | Vcc12  |       | l        | V                 |

|                      | active                             |                                         |        |       |          |                   |

# **ELECTRICAL CHARACTERISTICS** (continued) **Power Monitor and Negative Voltage Regulator** (continued)

| Symbol                                | Parameter    | Test Condition | Min. | Тур. | Max. | Unit |  |

|---------------------------------------|--------------|----------------|------|------|------|------|--|

| NEGATIVE VOLTAGE REGULATOR OSCILLATOR |              |                |      |      |      |      |  |

|                                       | Output swing |                | 1.2  |      | 4.8  | V    |  |

|                                       | Frequency    |                |      | 260  |      | kHz  |  |

## **Spindle Motor Driver.**

| Symbol    | Parameter                                                | Test condition                         | Min. | Тур. | Max. | Unit |

|-----------|----------------------------------------------------------|----------------------------------------|------|------|------|------|

| SPINDLE P | POWER SWITCH (SWPWR)                                     |                                        |      |      |      |      |

| VoL       | Low level output voltage                                 | Isink = 1mA                            |      |      | 1    | V    |

| VoH       | High level output voltage                                |                                        | 18   |      |      | V    |

| Tdhl      | Output voltage high to low delay time from NPOR          | Cload = 500pF<br>50% NPOR to Vout = 1V |      |      | 1    | μS   |

| Iswp      | Charge current                                           | Cload = 500pF                          |      |      | 9    | μΑ   |

| SPINDLE D | RIVER MODE CONTROL (SMODI                                | E)                                     |      |      |      |      |

| Vh12      | Voltage level for transition to test mode.               | Vcc5 = 5V<br>Vcc12 = 12V               | 7    |      | 9    | V    |

| Vh5       | Voltage level for BEMF sense in linear mode.             |                                        | 3.75 |      | 5    | V    |

| Vts       | Voltage level for induct. sense in linear mode.          |                                        | 2.25 | 2.5  | 2.75 | V    |

| V1        | Voltage level for BEMF sense in PWM mode.                |                                        |      |      | 1.25 | ٧    |

| Rints     | Input resistance.                                        |                                        | 7.5  |      | 50   | kΩ   |

| ttr       | Input rise and fall time.                                | 10%-90% Vcc5                           |      |      | 20   | ns   |

| SPINDLE S | TATE CONTROL INPUTS (SCNT                                | 1, SCNTL2, SCNTL3)                     |      |      |      |      |

| Vh        | High level input voltage                                 | CMOS LEVEL                             | 3.5  |      |      | V    |

| VI        | Low level input voltage                                  |                                        |      |      | 1.5  | V    |

| lin       | Input current                                            |                                        | -10  |      | 10   | μΑ   |

| BACK EMP  | COMPARATORS (SENU, SENVO                                 | OV, SENWIS)                            |      |      |      |      |

| Vie       | Common mode input voltage                                |                                        | 0    |      | 12   | V    |

| Vr        | Input voltage range where output shall not invert.       |                                        | -1   |      | 15   | V    |

| Voe       | Input offset voltage                                     |                                        | -4   |      | 4    | mV   |

| Vhe       | Hysteresis                                               |                                        | 2    |      | 10   | mV   |

| Vol       | Low level output voltage                                 | lout = -1mA                            |      |      | 0.5  | V    |

| Voh       | High level output voltage                                | lout = 1mA                             | 3.5  |      |      | V    |

| SPINDLE C | OUTPUT DRIVERS (SDRVU, SDRV                              | (V, SDRVW)                             |      |      |      |      |

| Rds(on)   | Total output ON resistance                               | lout = -1mA                            |      |      | 0.28 | Ω    |

|           | (Source + Sink)                                          | at 125°C                               |      |      | TBD  | Ω    |

| ldsx      | Output leakage current                                   | Idsx                                   |      | 1    |      | mA   |

| VcImp     | Clamp diode forward voltage                              | if = 1.0A                              |      |      | 1    | V    |

| Icros     | Current spikes during switching high or low side driver. | in PWM mode (guaranteed by design)     |      |      |      | mA   |

|           | SENSE AMPLIFIER (SISENH)                                 |                                        | 1    |      |      | 1    |

| Virange   | Current sense amplifier input voltage range              |                                        | 0    |      | 1.2  | V    |

| Gscs      | Current sense amplifier gain                             | Measured in test mode.                 | 5.82 | 6    | 6.18 |      |

| BW        | Current sense amplifier unity gain bandwidth.            | Guaranteed by design                   | 1.5  |      |      | MHz  |

| lin       | Input bias current                                       |                                        |      |      | 1    | μΑ   |

| Vofs      | Input offset                                             |                                        | 1    | 5.5  | 10   | m۷   |

# **ELECTRICAL CHARACTERISTICS** (continued) **Spindle Motor Driver.** (continued)

| Symbol                 | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Test condition                                   | Min.    | Тур.              | Max. | Unit           |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|-------------------|------|----------------|--|

| CURRENT                | SENSE COMPARATOR (SENIUS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |         |                   |      |                |  |

|                        | Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  | 48      | 60                | 72   | m۷             |  |

|                        | Input offset voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  | -6      |                   | 6    | mV             |  |

|                        | Response time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |         |                   | 400  | ns             |  |

| CURRENT                | CONTROL LOOP COMPENSATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N (SCOMP)                                        |         |                   |      |                |  |

| gm                     | OTA amplifier transconductance gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                  | 485     | 768               | 823  | μA/V           |  |

| Ccmp1<br>Ccmp2<br>Rcmp | External network at SCOMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |         | TBD<br>TBD<br>TBD |      | nF<br>nF<br>kΩ |  |

| Gsi                    | Transconductance gain: lout / SPWMFLT input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Rsense range = Rs $(0.12 \text{ to } 0.4)\Omega$ | -4%     | 1/6Rs             | 4%   | A/V            |  |

|                        | Gain linearity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Vin = 0.1 to 0.9 Vref                            | -1      |                   | 1    | %              |  |

|                        | Voltage at SPWMFLT to command zero output current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Imotor = 0                                       | 0       |                   | 80   | mV             |  |

|                        | Operating voltage range at SPWMFLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  | 0       |                   | 5    | V              |  |

|                        | Maximum motor current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPWMFLT = Vref                                   | 0.65/Rs |                   |      | Α              |  |

|                        | Current loop bandwidth from SPWMFLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Guaranteed by design                             | 15      |                   |      | kHz            |  |

| IiSPWM                 | Input bias current SPWMFLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  |         |                   | -3   | μА             |  |

|                        | Power supply rejection ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f < 10kHz, rip. < 0.3V<br>Imotor > 0.2A          | 60      |                   |      | dB             |  |

| OUTPUT D               | RIVERS SLEW CONTROL (SLWC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TL)                                              |         |                   |      |                |  |

| Rslew                  | External resistor at SWCTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  | TBD     | 100               | TBD  | kΩ             |  |

| SRhon                  | SDRV_X output voltage slew rate during switching high side driver on in linear mode or switching high driver on or off in switch mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $Lm = 0.3mH$ $R_{Load} = 1.2\Omega$              | TBD     | 10                | TBD  | V/µs           |  |

| SRhoff                 | SDRV_X output voltage slew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Lm = 0.3mH                                       | TBD     | 0.3               | TBD  | V/ms           |  |